CPU: Difference between revisions

Jump to navigation

Jump to search

No edit summary |

No edit summary |

||

| Line 16: | Line 16: | ||

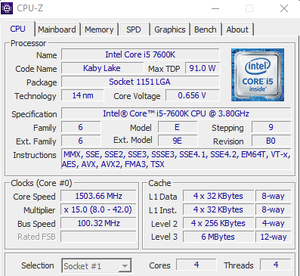

MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, EM64T, VT-x, AES, AVX, AVX2, FMA3, TSX | MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, EM64T, VT-x, AES, AVX, AVX2, FMA3, TSX | ||

OS (BSD/Linux/Windows etc): uses MMU Memory Management Unit | |||

RTOS: Task scheduler. | |||

Revision as of 05:52, 13 October 2023

Fairchild, Intel, Motorola, TI, MOS, Zilog, Sun, Dec, IBM, ARM

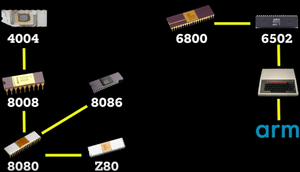

Fairchild IC's (traitorous eight) Intel 4004, 8008, 8088 Zilog Z80 Motorola 6800 MOS 6502 Acorn ARM

RISC Berkley / IBM MIPS Stanford IBM PowerPC SUN Sparc DEC Alpha

MMX, SSE, SSE2, SSE3, SSSE3, SSE4.1, SSE4.2, EM64T, VT-x, AES, AVX, AVX2, FMA3, TSX

OS (BSD/Linux/Windows etc): uses MMU Memory Management Unit

RTOS: Task scheduler.